处理器负责从内存读取数据,并利用数据执行加法等处理。指示执行这些处理的就是“指令”。指令有以下几种:进行加法的ADD指令,进行乘法的MULT(multiply)指令,以及读写内存的LOAD指令、STORE指令等。让我们看看这些指令是怎样规定的。

前面说过,指令架构详细地规定了处理器应当支持哪些指令、各个指令应执行什么操作等。

“架构”这个词源于建筑术语,意思是建筑的基本设计,现在被挪用到计算机的基本设计中,表示指令的设计、结构等。

拿汽车打比方,可以把指令架构想象成这样:发出向右打方向盘的指令,汽车就向右转;发出踩油门的指令就加速;发出踩刹车的指令就减速。对于汽车来说,这些基本指令是通用的,而汽车大灯、转向灯(转向提示器)的操作,以及空调、导航的操作指令,则由各家公司自行设计。

至于处理器的情况,Intel和AMD的x86处理器、PowerPC、SPARC、ARM、MIPS等各处理器的指令系统的应用领域和各指令的位排列顺序都不一样,互相并不兼容,因此一个指令架构上的机器语言程序(后面详细介绍)无法在其他指令架构的处理器上运行。

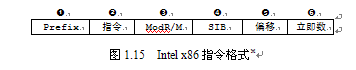

图1.15描述了Intel x86的指令格式。原来Intel/AMD的x86处理器只能处理8位和16位数据,架构扩展后才支持32位、64位数据。但是,指令中只有1比特用于区分8位指令还是16位指令,所以该比特被扩展为表示8位/32位切换或8位/64位切换。※ ModR/M为指定寄存器和内存的修饰符(ModR/M还有其他功能),SIB可能是Scale、Index、Base的缩写,不过Intel没有给出这些词汇的定义。

图1.15“Prefix”部分指定了是否要进行这种扩展。

图1.15的“指令”部分为ADD(加法)、MOV(内存与寄存器之间数据复制)等(后面会介绍其他指令)1~3字节长的指令种类。

如果进行运算的两个操作数(运算的输入数据)都是寄存器,那么可以用图1.15的“指令”栏表示这种情况;如果操作数位于内存中,就要用到下一个“ModR/M”栏(1字节)(图1.15)。

操作数位于内存中时,图1.15的“SIB”栏(1字节)可以用来指定地址计算的修饰方法,还可以利用图1.15的“偏移”栏指定1~4字节长的地址偏移。

如果不使用寄存器或内存,而是将常量作为操作数,就把它的值写到1~4字节的“立即数”栏(图1.15)。

并不是所有指令都有这些栏,不必要的栏位可以省略,所以叫做“可变长指令格式”。指令格式的长度将在第2章介绍。

Intel处理器的指令架构始于1978年发售的8086处理器。后来,Intel还发行了80186、80286、80386、80486等性能更高的处理器,因此连同后来的Pentium、Core处理器在内,这些处理器统称为x86。x86处理器的指令架构称为“x86架构”。

但是Intel对它正式称为IA-32(Intel Architecture-32),AMD的正式名称为AMD86架构。

计算机使用二进制,处理器的指令也由0和1组成。处理器依次读取内存中保存的指令,理解指令内容,然后执行指令的处理。这种处理器能够理解的指令格式称为“机器指令(Machine Instruction)”。

机器指令有以下几种:

—进行数据加减乘除的算术运算指令

—进行数据位运算的AND、OR、NOT等逻辑运算指令

—从内存读取数据的加载指令(Load Instruction)等

—向内存写入数据的存储指令(Store Instruction)等

此外,执行完一条指令后,处理器会读取下一个地址的指令并执行,但分支指令(Branch Instruction)可以更改下一个要执行的指令。而条件分支指令(Conditional Branch Instruction)可以判断前面的运算结果是0还是负数,只有在满足指定条件时才进行跳转,不满足条件时继续执行下一个地址的指令。

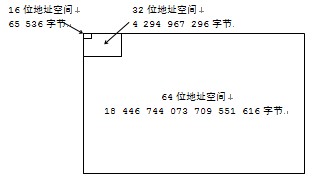

加载、存储指令等访问的内存都是有地址的。带有地址的内存排列成区间,就像现实世界中的开阔场地一样,因此把带有地址的区间整体称为地址空间。图1.16为16/32/64位地址空间的示意图。

图1.16 16/32/64位地址空间示意图

20世纪70年代的8位微处理器,访问内存时只能指定16位(0~65535)地址。因此能访问的最大内存容量也被限制在64KB之内。也就是说,这些处理器的地址空间是64KB。

可见,内存地址的位数与运算器、寄存器的位数大多数情况下是一致的,但这并不是必需的。例如,第一代x86处理器8086的内存地址只有16位,但加上偏移量(程序的起始地址)后变成20位,就可以访问1MB的地址空间。但是,8086上一个程序能使用的内存空间只有16位,运算器与寄存器也是16位,因此被称做16位架构。

另外,现在的处理器大都拥有64位运算器和寄存器,但还没有安装264字节内存的计算机,因此内存地址总线的实际宽度为40~48位左右。不过,这些处理器依然叫做64位架构。所以说,XX位架构并不是太严格的定义,根据常理判断就行了。

随着计算机安装的内存容量增加,8086的地址指定方式已不能访问所有内存。因此,Intel的Pentium处理器和各种RISC处理器都准备了32位运算指令,用32位指定内存地址。这些处理器的地址空间是4GB,不过4GB并不是指内存空间的大小,而是指这些处理器拥有32位地址空间。

32位地址可以访问4GB的内存,但说到底只是“可以指定4GB地址空间”,并不意味着计算机一定有4GB内存空间。事实上,第一个支持32位地址空间的处理器问世当初,计算机的实际内存容量不过几MB而已。而且,当时认为32位地址空间应该很宽裕了,哪知现在的服务器会安装16GB以上的内存,就连个人计算机也动不动就安装4GB以上的内存,因此32位地址空间明显不够用了。

64位地址空间——AMD86-64、Intel 64

20世纪90年代,RISC处理器(后述)增加了64位运算指令,开始支持64位地址空间。而x86系列中,AMD在2000年先行发表了名为AMD86-64的64位扩展架构,之后Intel也开始支持同一种架构。为了将64位扩展架构与原来的x86架构区别,通常称它为“x64架构”。

现在的计算机安装的内存达到几GB甚至数十GB,预计今后还会继续按照每三年增长四倍的速度发展,那么64位地址空间也将在40~45年后开始捉襟见肘。在那之前的10年内必须扩展地址空间,所以可以预见,从现在开始30~35年后,即2040—2045年间,就要采用支持128位地址空间的指令架构了。

本文节选自《支撑处理器的技术——永无止境地追求速度的世界》

(美)海撒安藤著;

李剑译

电子工业出版社出版

分享到:

相关推荐

ARM微处理的指令集--指令系统(较基础) 介绍了ARM处理器的寻址方式和ARM指令集

### 超标量和超长指令字处理器处理器简介 #### 超标量处理器结构及其相关问题 超标量处理器是一种先进的微处理器架构,它能够在一个时钟周期内执行多个指令,通过并行处理来提高处理器的性能。这种设计的核心在于...

ARM处理器的指令系统是其架构的核心组成部分,它不仅定义了处理器如何执行操作,还决定了程序的效率和可读性。ARM处理器,特别是ARM7TDMI-S,采用了精简指令集计算机(RISC)的设计理念,这使得其指令集和译码机制...

【多发射处理器的指令调度算法】是现代计算机处理器设计中的一个重要研究领域,旨在提升处理器性能。随着VLSI工艺的快速发展,计算机设计思路发生了变化,RISC(精简指令集计算机)技术因其高效的指令执行效率成为了...

总结,处理器指令集是计算机硬件和软件协同工作的关键,易语言通过源码方式获取处理器指令集信息,为开发者提供了深入理解和利用硬件资源的手段。理解并掌握处理器指令集的知识,对于提升软件开发水平和优化程序性能...

通过设计容量可配置的多缓存指令提交结构,实现存储器操作指令和ALU类型指令的分类退休,根据超标量处理器架构及性能需求对目标缓存和存储缓存容量进行参数化配置降低流水线阻塞风险,同时利用指令目的寄存器编码...

【关键词】涉及到的主要概念包括预取指令缓存、微指令和流水线,这些都是处理器设计中的关键组成部分。预取指令缓存用于提前加载即将被执行的指令,以减少处理器等待指令的时间,提高执行效率。微指令则是控制处理器...

《同时多线程处理器的指令调度器设计》一文主要探讨了在多核处理器背景下,如何设计一种高效且简单的动态指令调度器,以应对同时多线程(SMT,Simultaneous Multi-Threading)处理器中的指令级并行(ILP)和线程级...

通过学习和理解这段“易语言取处理器指令集”源码,开发者不仅可以掌握如何获取处理器信息,还能深入理解处理器指令集与软件开发的关系,为编写高效、兼容的程序提供基础。同时,这对于提升易语言程序员的底层系统...

"一种用于容错处理器的指令复制方法" 本文介绍了一种用于容错处理器的指令复制方法,旨在解决处理器中的容错机制问题。该方法通过修改超标量处理器架构,利用时间冗余技术实现指令复制,从而检测处理器中的控制流...

然而,随着x86处理器架构的不断发展,如Intel的NetBurst、Yonah和Core微架构等,微指令的数量和复杂性都在不断增加,这就需要引入微指令融合和宏指令融合技术,以提高处理器效率,这些技术的引入进一步增加了微指令...

在IT领域,Intel处理器的CPUID指令是程序员和硬件工程师们深入理解处理器特性和功能的重要工具。这份由Intel发布的文档,即"Intel® Processor Identification and the CPUID Instruction Application Note 485",...

【标签】中的“单片微机原理及应用第3章9处理器”进一步强调了这个主题的针对性,即在学习单片机原理时,重点关注处理器控制指令的掌握和应用。 【压缩包子文件的文件名称列表】中的“赚钱项目”与本主题看似无关,...

《S698系列处理器中指令流水的设计与实现》这篇技术文章主要探讨了现代高性能处理器中的关键技术——指令流水线的设计原理和实现方法,特别是在S698系列处理器中的应用。指令流水线是一种将处理过程划分为多个独立...

ARM专利:超标量处理器的指令发出控制

"易语言取处理器指令集源码"是易语言中用于获取处理器支持的指令集的相关源代码,这对于理解计算机底层工作原理和优化程序性能具有重要意义。 处理器指令集是计算机硬件与软件之间的桥梁,它定义了处理器能执行的...

标题中的“自制CPU处理器 MIPS指令集 五级流水 带溢出 不带乘除”涉及到了几个关键的计算机科学概念,这些概念是理解和构建基于MIPS架构的CPU的基础。 首先,MIPS(Microprocessor without Interlocked Pipeline ...

Xtensa架构是一系列32位RISC处理器指令集架构,被用于嵌入式系统设计中。该架构支持广泛的指令类型,涵盖了从基础的数据处理到复杂的控制流程指令。本文档对Xtensa架构中的核心指令进行了分类和详细介绍,包括加载...

3. **哈佛结构或冯诺依曼结构**:MIPS 架构可以采用这两种内存体系之一,前者将指令和数据存储在独立的高速缓存中,后者则共享同一存储空间。 4. **多种寻址模式**:支持立即寻址、直接寻址、间接寻址等多种寻址方式...