哈尔滨理工大学软件工程专业08-7李万鹏翻译作品,转载请标明出处

http://blog.csdn.net/woshixingaaa/archive/2011/03/16/6252330.aspx

文档整理自ARM System Developer's Guide

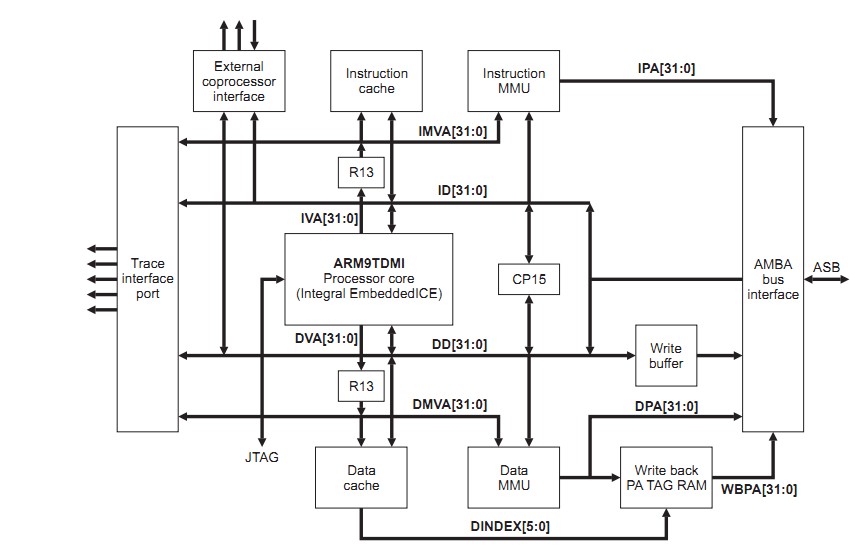

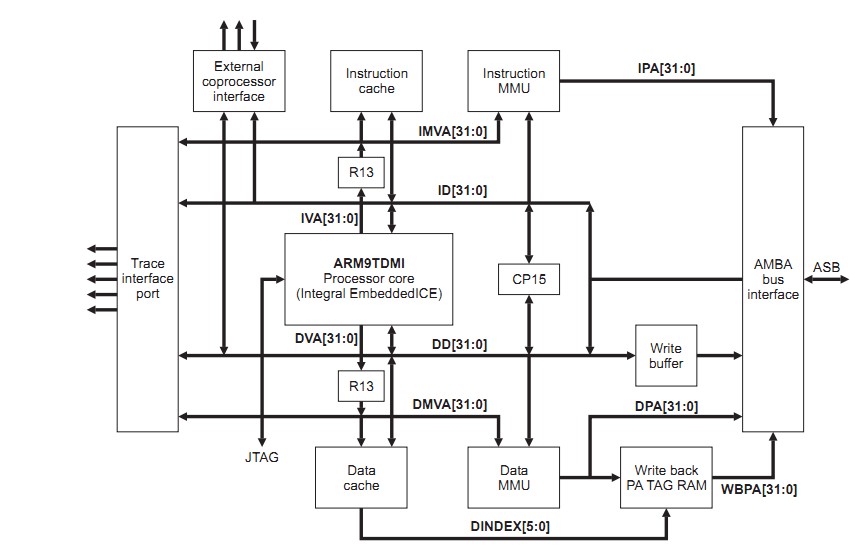

ARM920T处理器包含了ARM9TDMI内核,ARM9TDMI实现了ARM architecture v4T。

ARM920T处理器包含两个协处理器:

CP14。用于调试

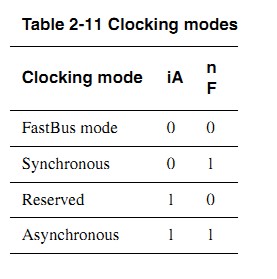

CP15。系统控制协处理器,提供附加的寄存器用来配置和控制cache,MMU,保护系统,时钟模式,和ARM920T其他的系统选项,如大小端操作。你可以使用MCR,MRC访问定义在CP15中的寄存器。

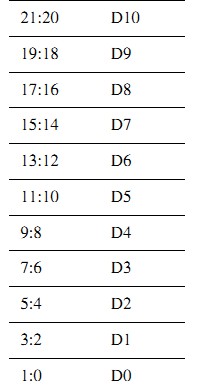

CP15定义了16个寄存器,寄存器的映射图如下:

注:寄存器位置0可以访问两个寄存器,通过opcode_2的值来确定。

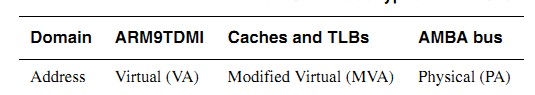

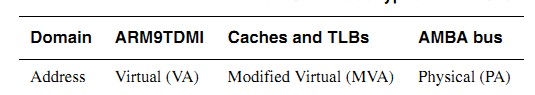

ARM920T存在3个地址。

只能在特权模式下使用MCR和MRC指令访问CP15。这些指令的格式是:

MCR/MRC{cond} P15,,Rd,CRn,CRm,

指令CDP,LDC,STC和非特权模式的MRC,MCR指令操作CP15会导致未定义指令异常。MRC和MCR指令的CRn域指定了要访问的协处理寄存器。opcode_1,和CRm域应该是0,除非值被指定用来选择需要的操作。

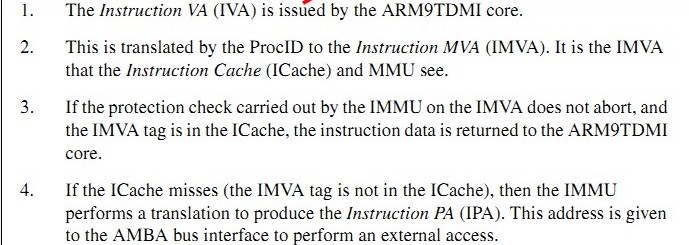

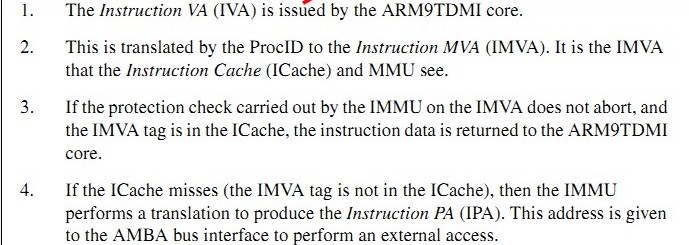

Register 0,ID code register

可以通过读CP15 register 0,opcode_2域设置成除了1的任何值(在读的时候CRm应该为0)。

如:

MRC p15,0,Rd,c0,c0,0;return ID register

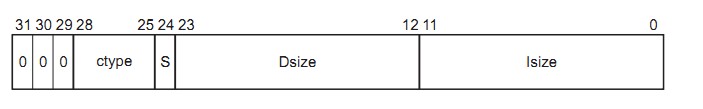

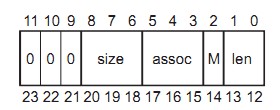

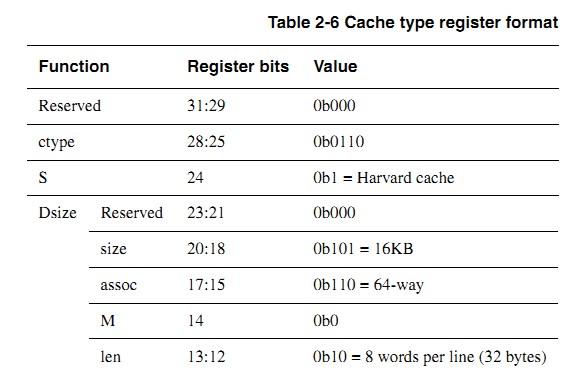

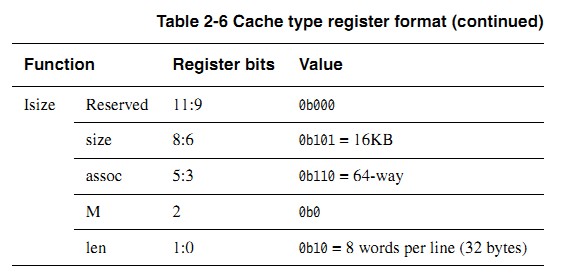

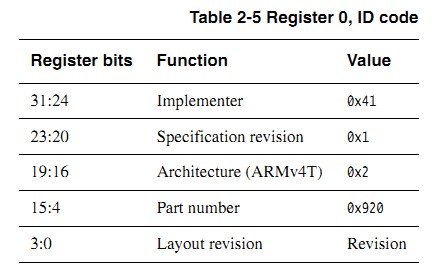

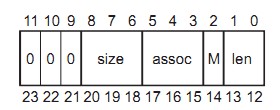

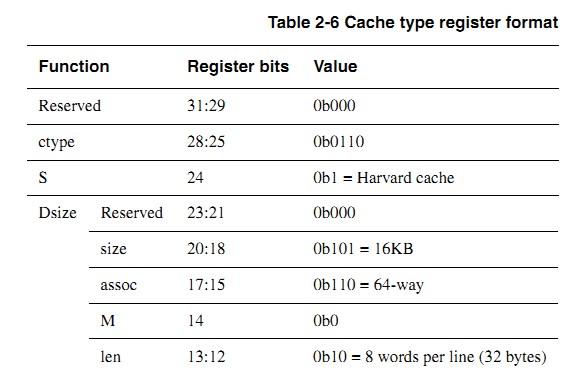

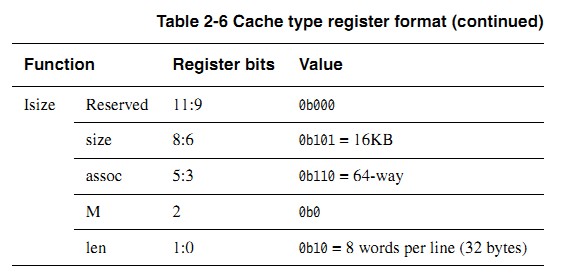

cache type register 0

包含cache的大小和体系结构的信息。可以通过设置域为1,读CP15 register 0来访问cache type register。例如:

MRC p15,0,Rd,c0,c0,1;returns cache details

Dsize和Isize域格式一样:

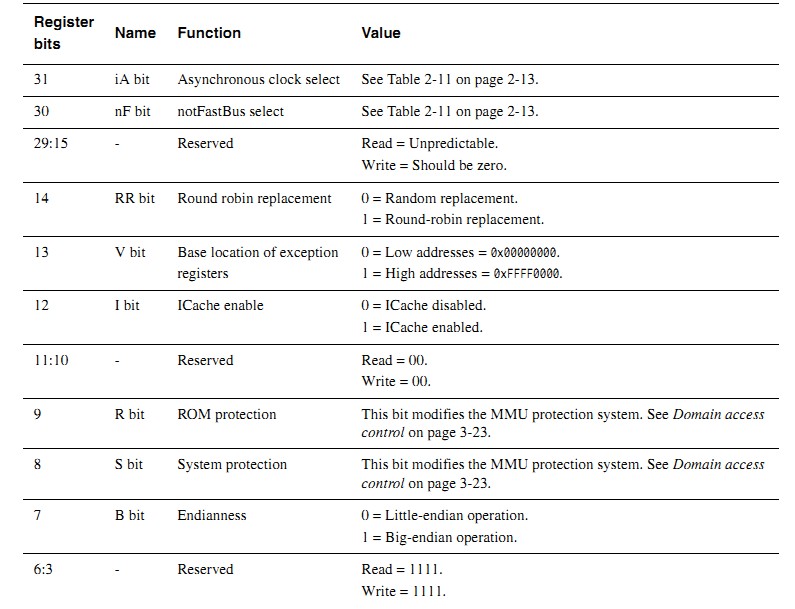

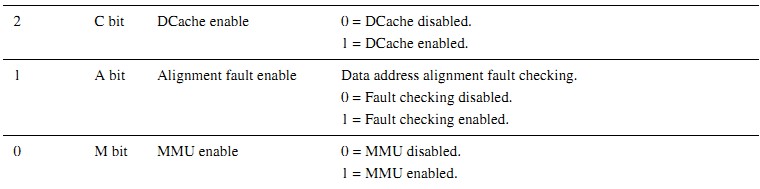

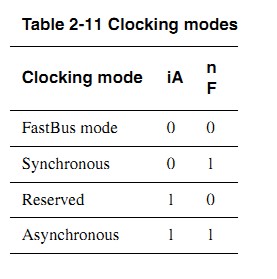

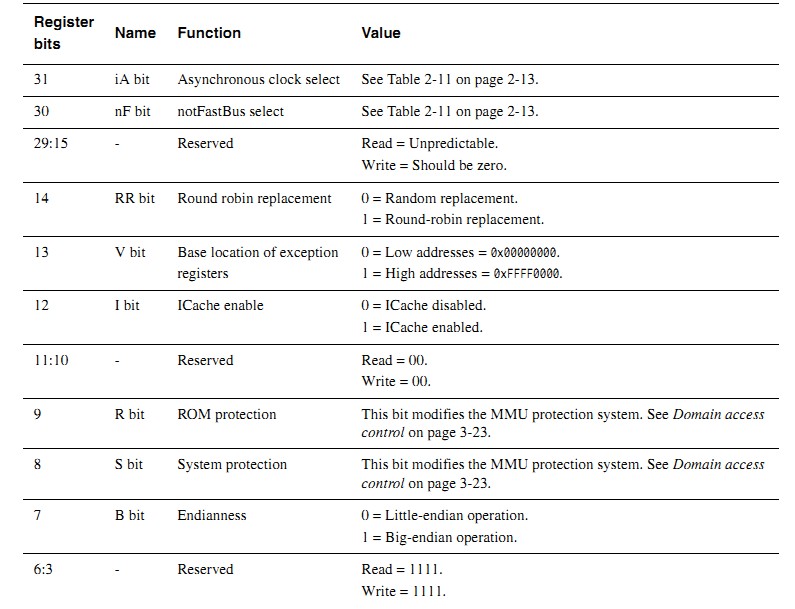

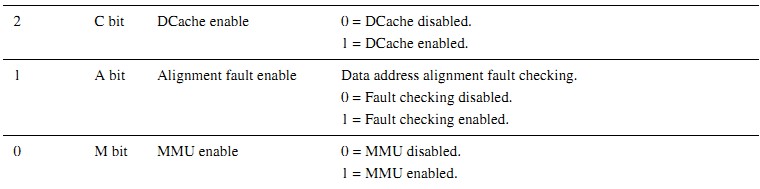

Register1,control register

这个寄存器包含了ARM920T的控制位。

MRC p15,0,Rd,c1,c0,0 ;read control register

MCR p15,0,Rd,c1,c0,0;write control register

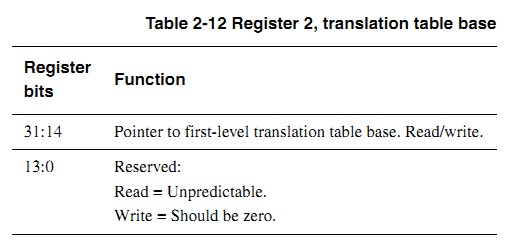

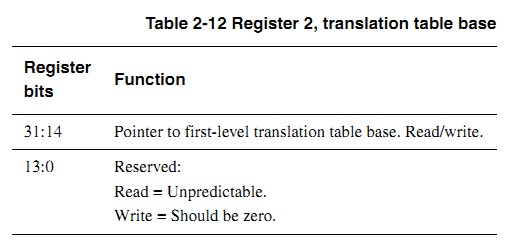

Register 2,translation table base(TTB)register

这个是页表基址寄存器。

使用下面的指令访问TTB:

MRC p15,0,Rd,c2,c0,0;read TTB register

MCR p15,0,Rd,c2,c0,0;write TTB register

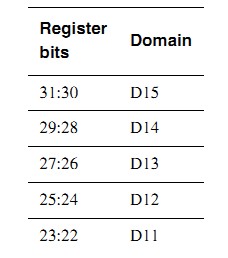

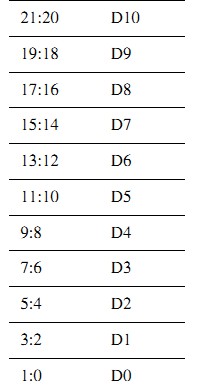

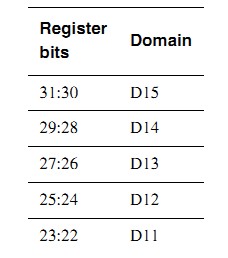

Register 3,domain access control register

这个是读写域访问控制寄存器。

MRC p15,0,Rd,c3,c0,0;read domain 15:0 access permissions

MCR p15,0,Rd,c3,c0,0;write domain 15:0 access permissions

Register 4,reserved

Register 5,fault status registers

Register 6,fault address registers

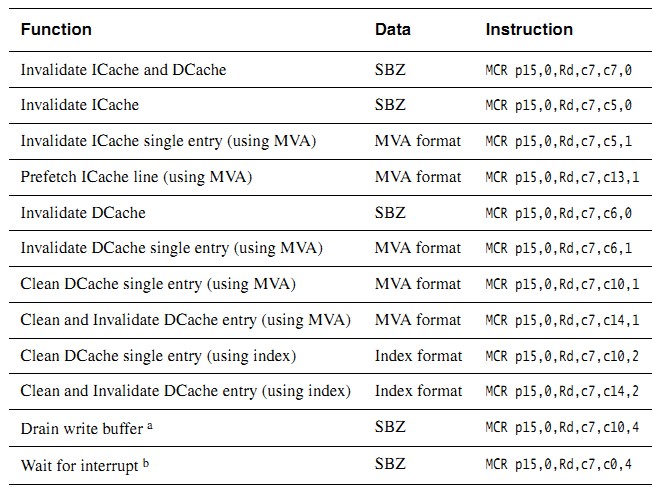

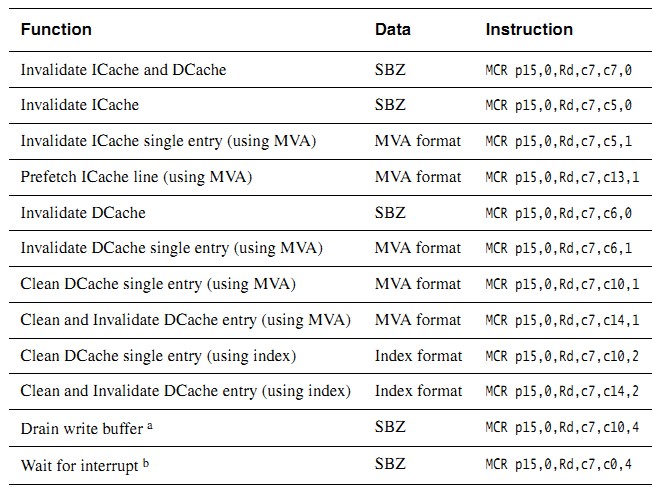

Register 7,cache operations register

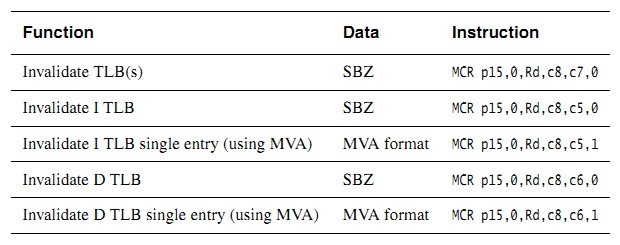

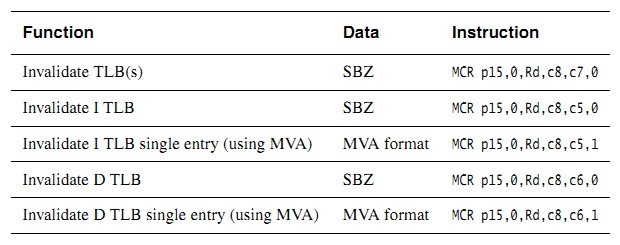

Register 8,TLB operations register

用来管理Translation Lookaside Buffers(TLBs),指令TLB和数据TLB。

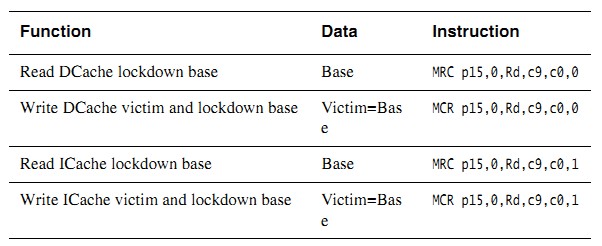

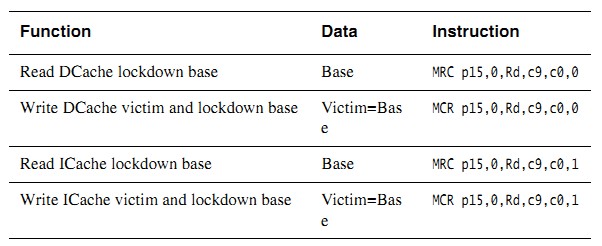

Register 9,cache lockdown register

opcode_2=0x0 访问的是Dcache

opcode_2=0x1 访问的是 Icache

Regiter 10,TLB lockdown register

opcode_2=0x0 访问的是D TLB

opcode_2=0x1 访问的是 I TLB

Register 11,12,and 14,reserved

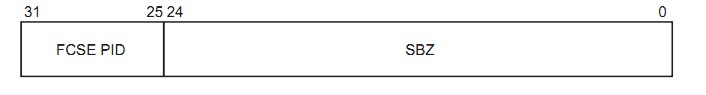

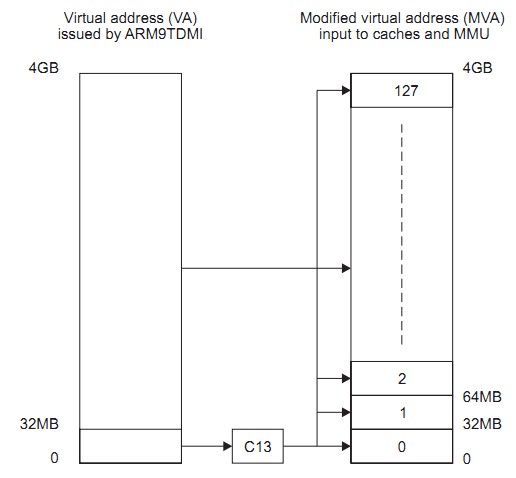

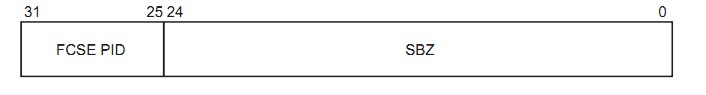

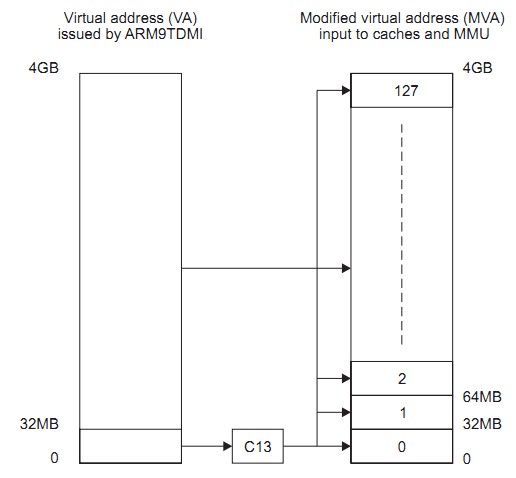

Register 13,FCSE PID register

是快速上下文切换扩展寄存器。

MRC p15,0,Rd,c13,c0,0;read FCSE_PID

MCR p15,0,Rd,c13,c0,0; write FCSE_PID

ARM9TDMI发出的地址在0~32MB范围内的被CP15的register 13转换。地址A变成A+(FCSE_PID×32MB)。FCSE_PID是一个7位的域,能够使128×32MB的进程被映射。

Register 15,test configuration register

分享到:

相关推荐

### ARM协处理器CP15详解 #### 一、概述 ARM协处理器是ARM体系结构中的一个关键组成部分,它被设计来扩展ARM处理器的功能,并能够处理特定类型的数据或执行专门任务,比如浮点运算、图形处理或者加密解密等。ARM...

本文将深入探讨ARM协处理器的使用和介绍,特别是针对ARM920T处理器中的协处理器特性。 ARM920T是一款32位微处理器,支持多种协处理器,以提高系统的性能和灵活性。其中,它包含两个主要的协处理器:CP14和CP15。CP...

#### ARM920T的CP15协处理器 CP15是ARM架构中的一种协处理器,用于配置和控制MMU、Cache等硬件特性。在ARM920T中,CP15主要用于控制MMU的设置,例如设置页表基址寄存器(Page Table Base Register, PTBR)等。 ###...

在ARM920T处理器中,有两个重要的协处理器实例:CP14和CP15。CP15是系统控制协处理器,负责配置和控制如缓存、MMU、保护系统以及时钟模式等系统级功能。它拥有15个特定的寄存器,通过MCR和MRC指令进行访问,比如ID号...

CP15是ARM处理器的协处理器寄存器,用于控制和查询处理器的高级特性,如MMU、CACHE、虚拟地址映射等。它包含一系列寄存器,如控制寄存器、状态寄存器和系统寄存器,能够进行系统配置和调试。通过访问CP15寄存器,...

在ARM体系中,最多可以有16个协处理器,其中`ARM::CP15`是系统控制协处理器的标准类,处理MCR和MRC指令。对于具体CPU的协处理器实现,如`ARM::ARM7_CP15`和`ARM::XScale_CP15`,它们需要定义MCR和MRC方法。 `ARM::...

ARM920T的MMU架构主要依赖于协处理器CP15,CP15提供了对MMU的控制和配置接口。 **ARM920T CP15协处理器** - **CP15**:专门用于控制和配置MMU及其他内存管理相关的硬件特性。 - **MMU配置**:通过向CP15发送特定...

ARM920T是在ARMTDMI的基础上分别增加了16k的指令和数据Cache、数据和指令存储器管理单元MMU、写缓冲器及协处理器CP15,各单元之间通过AMBA(Advanced Microcontroller Bus Architecture)总线同总线主控单元相连。...

- **两个内部协处理器**:CP14用于调试控制,CP15用于存储系统控制及测试控制。 #### 实现细节 为了构建完整的嵌入式系统,除了$3C2410处理器外,还需要配合以下组件: - **Flash电路**:用于存储系统引导程序和...

ARM920T核内部还包含两个协处理器CP14和CP15,分别用于调试控制和存储系统控制等。 在控制系统硬件设计方面,本系统选择了S3C2410作为ARM微控制器。S3C2410是三星公司生产的一款ARM9系列处理器,其最高运行频率达到...

- **协处理器**:CP14用于调试控制,CP15用于存储系统控制和测试控制。 2. **集成的内部电路和外围接口** - **LCD控制器**:支持STN和TFT类型的液晶显示屏,可用于实现图形界面。 - **SDRAM控制器**:用于管理和...

在ARM920T处理器中,CP15协处理器负责管理MMU和Cache的操作。通过特定的指令,操作系统可以在启动时配置和控制这些功能。例如,设置页表以建立虚拟地址到物理地址的映射,以及初始化和管理Cache,包括清除、填充和...

- **协处理器**:配备两个协处理器,CP14用于调试控制,CP15则负责存储系统控制与测试控制。 - **高速缓存**:独立的16KB地址缓存与16KB数据缓存,显著提高数据访问速度。 - **MMU**:管理虚拟内存,优化多任务处理...

例如,Cortex-A8使用ARMv7架构,但仅使用了其中的cp14和cp15两个协处理器。 目前市场上流行的体系架构包括X86、MIPS和ARM。ARM架构由于其低功耗和高性能的特性,在嵌入式领域广泛应用于处理器产品,如ARM920t、...