<script>function StorePage(){d=document;t=d.selection?(d.selection.type!='None'?d.selection.createRange().text:''):(d.getSelection?d.getSelection():'');void(keyit=window.open('http://www.365key.com/storeit.aspx?t='+escape(d.title)+'&u='+escape(d.location.href)+'&c='+escape(t),'keyit','scrollbars=no,width=475,height=575,left=75,top=20,status=no,resizable=yes'));keyit.focus();}</script>

作者:刘洪涛,华清远见嵌入式培训中心高级讲师,ARM ATC授权培训讲师。

最近计划针对我们华清远见的教学开发一套PXA270系统,我把我的一些软、硬件开发过程记录下来和大家一起分享、讨论。有好的建议大家一定要及时交流,lht@farsight.com.cn。上一篇我写了“PXA270嵌入式系统设计一:电源管理部分”,今天接着写一下关于时钟及复位部分的内容,欢迎指正~~

一、时钟部分

任何一款处理器都需要至少一个时钟源。在处理器的内部会有相应的时钟管理单元来为cpu及各个功能控制单元提供合适的时钟。

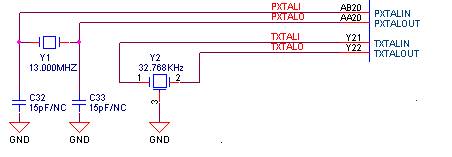

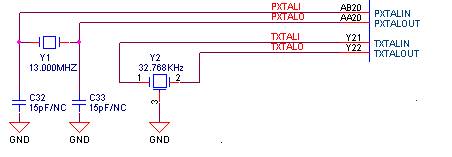

PXA270处理器的需要两个外部振荡器,1个13M和1个32.768K。它们各自的作用:

- 13M的时钟主要用于产生系统各个PLL的参考时钟,也可以为部分低速控制器提供时钟;

- 32.768K的时钟主要用于为RTC控制器提供实时时钟源,也可以为部分低速控制器提供时钟。

PXA270处理器内部有两个PLL单元,一个是外围PLL,另一个是核心PLL

- 外围PLL使能后产生固定的312M时钟,用于为高速控制器提供时钟源;

- 核心PLL可以产生26—624M时钟,用于cpu、内存控制器、系统总线、及LCD控制器。

时钟部分的电路原理图:

二、复位部分

PXA270提供了5种复位方式:

- 上电复位:当VCC_BATT管脚第一次上电时产生,是一种完全复位。

- 硬件复位:也是种完全复位,当nRESET管脚置位时产生。

- 看门狗复位:看门狗控制器触发,是一种部分复位,详见PXA270芯片手册。

- GPIO复位:是硬件复位的一种形式,可以由外部信号触发。也是一种完全复位。

- 睡眠退出复位:复位那些在睡眠和深度睡眠时断电的模块。

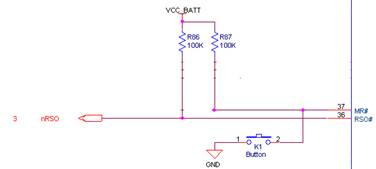

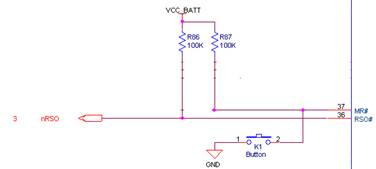

系统中和复位相关的电路原理图。

下图是max1586C和系统复位电路相关的接线

K1为复位按键,通过max1586C的复位管理电路输出nRSO信号。如果系统没有类似max1586C的复位管理电路的话,可以用一片类似max811的复位芯片来完成,也可以用阻容及一些逻辑电路的方式来完成复位。

注意:max1586C的MR脚复位会复位max1586C的V3输出到1.3V,对其它电压输出没有影响。

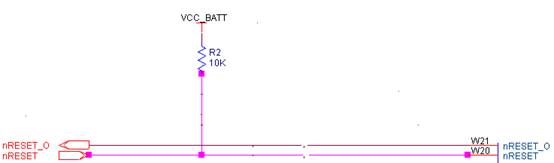

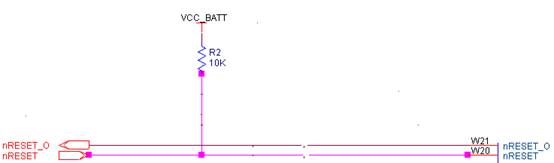

下图是复位信号和PXA270的nRESET的接线。

当nRESET置位或看门狗控制器复位时,nRESET_O都可以置位。可以用其来完成其它外围芯片的复位。

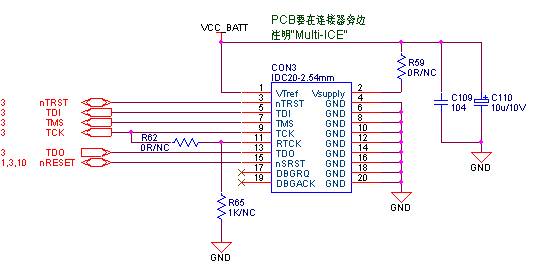

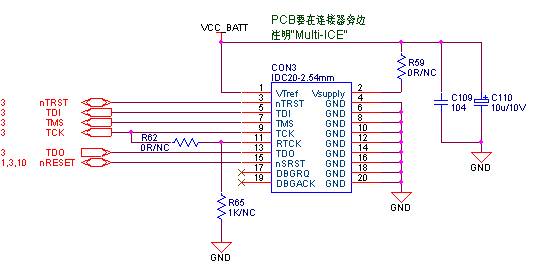

下图是JTAG电路,其复位信号要和系统的nRESET连接。

时钟复位部分大致就这么多了。

分享到:

相关推荐

本篇文章主要探讨了PXA270嵌入式系统设计中的时钟管理和复位机制,这对于系统稳定运行至关重要。 首先,时钟部分是处理器正常工作的基础。PXA270处理器需要两个外部振荡器,一个13MHz(MHz,兆赫兹)和一个32.768...

PXA270 U-Boot源码是针对Marvell公司生产的PXA270处理器的引导加载程序的源代码,它在嵌入式系统开发中扮演着至关重要的角色。U-Boot是一款流行的开源引导加载程序,它为多种处理器平台提供了启动服务,包括加载操作...

1. **CPU模块**:PXA270处理器的核心部分,包括时钟发生器、电源管理电路、复位电路等。这些电路确保了处理器正常启动和运行,并且可以在不同工作模式下切换,以优化功耗。 2. **内存接口**:PXA270支持SDRAM和SRAM...

1. **初始化模块**:这部分代码负责初始化PXA270处理器上的SDHC控制器,包括配置时钟、中断处理、DMA通道设置等。这是驱动程序的基础,确保了硬件层面与软件的正确交互。 2. **I/O操作**:这部分包含了读写命令的...

**PXA270定时器详解** ...通过实际的代码实践,可以加深对定时器工作原理的理解,提高系统设计的效率和可靠性。在实际应用中,根据项目需求选择合适的定时器类型和配置,可以有效提升系统性能和稳定性。

Boot Loader是嵌入式系统中的关键组件,负责在系统加电或复位后初始化硬件环境,加载操作系统内核,并将其传递到适当的内存位置以便执行。在PC系统中,Boot Loader的工作通常由BIOS和硬盘上的MBR(主引导记录)中的...

它具有高性能、低功耗的特点,广泛应用于嵌入式系统设计中。而EBOOT针对PXA255的定制,意味着我们需要了解PXA255的内存管理、中断处理、GPIO(通用输入/输出)配置等相关知识。 EBOOT程序通常分为两部分:引导加载...

综上所述,《PXA255设计文档_原理图_布局图》是一份非常宝贵的资源,对于想要深入学习嵌入式开发的人来说,这份文档不仅可以提供硬件层面的基础知识,还能帮助理解复杂的系统架构和技术细节。通过掌握这些知识,...

【PXA255处理器最小系统硬件设计】 PXA255处理器是Intel公司基于Xscale微架构设计的一款高性能嵌入式处理器,适用于新一代无线手持设备。它集成了多种功能模块,包括内存控制器、LCD控制器、DMA控制器、音频接口、...

PXA168是Marvell公司推出的ARMADA 16x系列应用处理器家族的一员,专为高性能、低功耗的嵌入式系统设计。它集成了多种先进的处理单元和接口,如ARM架构的CPU核心、图形处理器、视频编解码器、多媒体加速器以及高速...

Bootloader作为嵌入式系统启动过程中的关键组件,它的主要任务是在系统加电或复位后初始化硬件,如内存控制器、时钟、串口等,然后加载操作系统内核到内存中以便执行。 Bootloader的设计与实现涉及以下几个重要环节...

在设计ARM系统的最小系统时,通常需要考虑以下几个关键组件:处理器(此处为PXA270)、电源管理、存储器(如SRAM和SDRAM)、时钟信号源、复位电路以及基本的输入/输出接口。例如,PXA270的片上存储器接口配置图展示...

本文主要探讨的是如何为基于嵌入式Linux的操作系统设计触摸屏驱动程序,以提升用户体验并确保系统的高效稳定运行。作者孟桂芳在文中介绍了使用Intel PXA255处理器为核心的硬件平台,并选择了嵌入式Linux作为操作系统...

首先,ARM7是ARM公司设计的一款32位RISC(精简指令集计算机)处理器内核,广泛用于移动设备、嵌入式系统和网络设备。其特点是高性能、低功耗,支持Thumb指令集,可以运行在多种不同类型的硬件平台上。 AT91FR40162...

1. **初始化硬件**:Bootloader首先要进行CPU复位后的硬件初始化,包括时钟设置、内存控制器配置、GPIO、中断控制器等,确保系统运行的基础环境。 2. **引导加载器启动**:Bootloader通常分为两个阶段。第一阶段...

- **开发环境**: 使用ARM Developer Suite (ADS) 开发环境进行嵌入式系统设计。 - **关键技术**: 包括处理器的初始化、存储器管理、中断配置等。 #### 三、Bootloader设计流程 - **阶段划分**: - **阶段1**: 采用...