一)前期准备

*FTP客户端软件

*Xmanager

*pl/sql dev

*10gr2_db_sol[1].cpio,数据库安装程序,适用于SUN Solaris(SPARC),数据库版本10.2。

二)创建用户组、用户

1)添加用户组:

# groupadd oinstall

# groupadd dba

2)添加用户:

# useradd –g oinstall –G dba –d /export/home/oracle –s /bin/csh –m oracle

{-g表示用户所属组、-G表示用户所属附加组、-d表示用户主目录、-s表示用户默认shell类型、oracle表示用户名,-m参数表示自动创建此用户的主目录,为避免麻烦,请勿手动创建此目录}

# passwd oracle

{表示为oracle用户设置密码,输入该命令并回车之后,系统会提示输入密码、确认密码}

三)创建Oracle数据库安装点

新建目录,Oracle将安装于这些目录下:

# mkdir /opt/oracle

# mkdir /opt/oracle/product/10gr2

# mkdir /opt/oracle/doc

并把/opt/oracle目录属主改为oracle,属组改为oinstall:

# chown -R oracle:oinstall /opt/oracle

{附Solaris系统目录说明

/: root文件系统

/bin:可执行程序,基本命令

/usr:UNIX系统文件

/dev:设备文件(逻辑设备)

/devices:设备文件(物理设备)

/etc:系统配置,系统管理数据文件

/export:允许其他系统访问的目录和文件

/home:用户家目录

/kernel:系统核心模块

/lib:系统库

/opt:增加的一些应用软件

/tmp:SWAP区

/var:系统的一些管理文件}

四)修改Oracle用户的环境变量

以oracle用户登陆,在oracle用户的主目录下找到并修改它的环境变量.cshrc(这是一个隐藏文件,ls时须加-a参数)。如未发现此文件,请使用cp命令将主目录下的local.cshrc文件拷贝一份另命名为.cshrc。

在.cshrc文件的umask 022下一行添加如下内容

setenv ORACLE_BASE /opt/oracle

setenv ORACLE_HOME /opt/oracle/product/10gr2

setenv ORACLE_SID yoursid

setenv ORACLE_UN system

setenv ORACLE_PW yourpassword

setenv NLS_LANG "simplified chinese_china.ZHS16GBK"

setenv NLS_DATE_FORMAT "YYYY-MM-DD HH24:Mi:SS"

{ORACLE_BASE是Oracle根目录,ORACLE_HOME是Oracle产品目录,即如果你的机器装两个版本的Oracle系统,可以在同一个ORACLE_BASE下,但ORACLE_HOME会做两个。}

之后,在path的开头位置加入$ORACLE_HOME/bin

例如: set path=($ORACLE_HOME/bin /usr/ccs/bin /bin /usr/bin ) 请照此原样填写,勿使用绝对路径。

使新环境变量生效:

# source .cshrc

校验环境变量:

# env

五)修改Solaris系统参数

1)使用root账户登录,创建/etc/system文件的一个备份,例如:

# cp /etc/system /etc/system.orig

2)编辑/etc/system,在最后添加如下:

set noexec_user_stack=1

set semsys:seminfo_semmni=300

set semsys:seminfo_semmns=1050

set semsys:seminfo_semmsl=400

set semsys:seminfo_semvmx=32767

set shmsys:shminfo_shmmax=6400000000(服务器8G内存的情况下,不同情况按比例增减)

set shmsys:shminfo_shmmin=1

set shmsys:shminfo_shmmni=300

set shmsys:shminfo_shmseg=30

3)重启系统使参数生效:

# /usr/sbin/reboot

六)Oracle系统安装

1)使用oracle用户登录ftp,将安装程序10gr2_db_sol[1].cpio上传至oracle用户主目录。

2)解压

# gunzip -d 10gr2_db_sol.cpio.gz //(added by editor)

# cpio –idmv < 10gr2_db_sol.cpio

如解压时报错,则换成root账户解压。

3)以oracle用户登录,执行

# ./runInstaller

如果不能执行的话,切换成oracle用户执行shell具体命令为:

# su oracle

# ./runInstaller

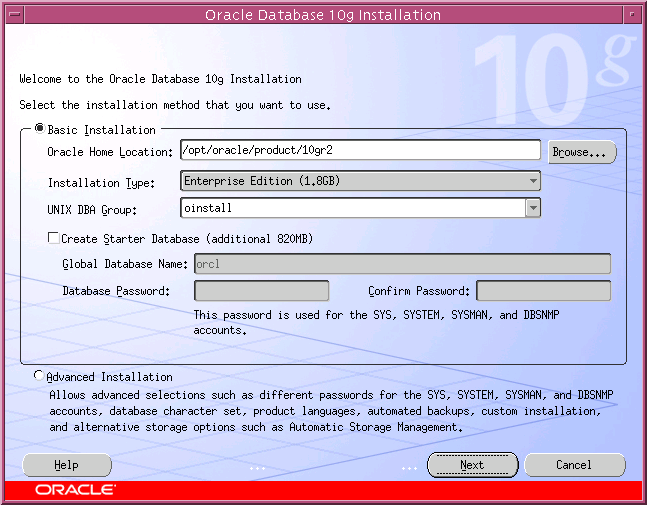

第一步:注意不选“Create Starter Database”

第二步:操作系统检查

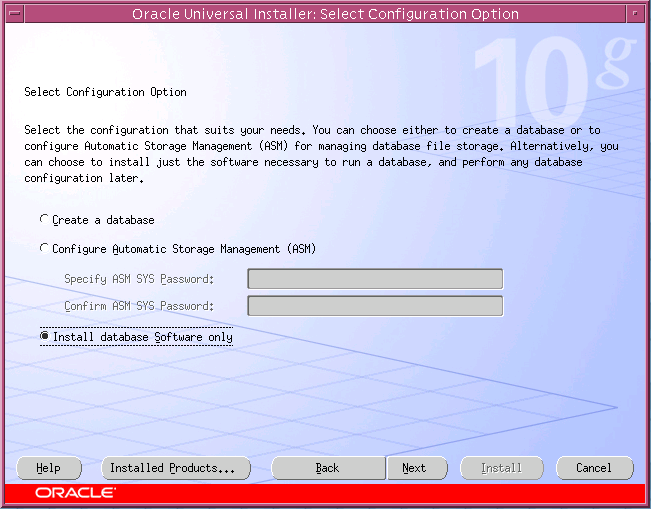

第三步:选择配置选项

第四步:显示安装信息汇总

第五步:显示安装进度

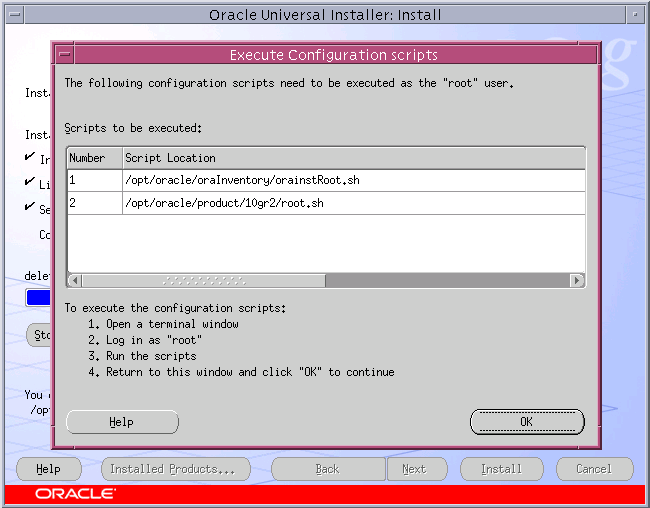

第六步:安装中途,提示执行脚本文件,以root用户执行之。

第七步:显示Oracle软件安装完成界面。

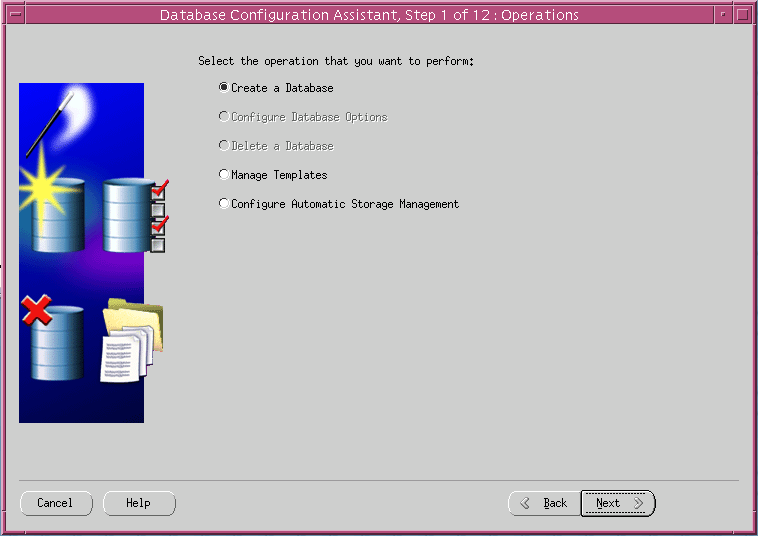

第八步:于oracle/product/10gr2/bin目录下执行./dbca,出现创建数据库界面。

第九步:选择建库模板,默认

第十步:配置数据库服务名

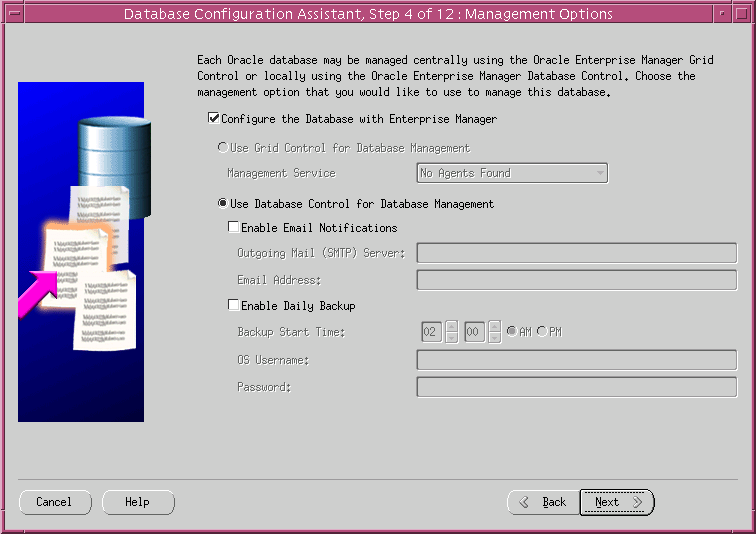

第十一步:开始数据库配置

第十二步:为系统账户设置密码(为简便起见,可以都设置为一样的密码)

第十二步:为系统账户设置密码(为简便起见,可以都设置为一样的密码)

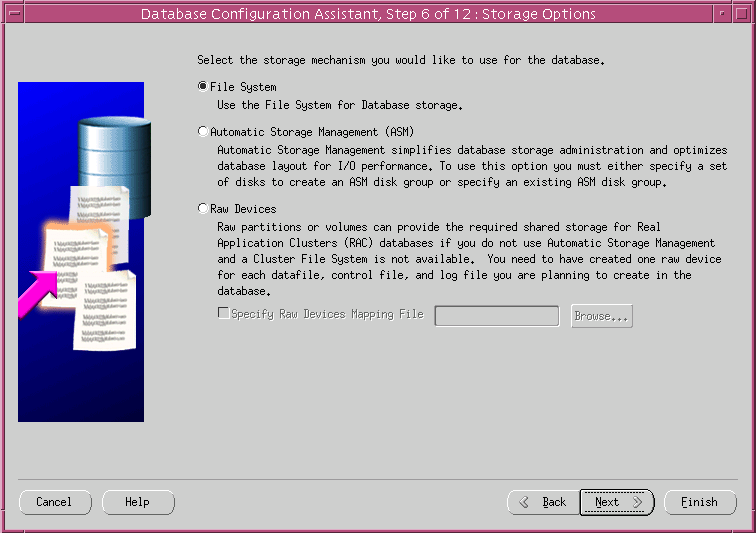

第十三步:设置存储机制,这里选择的是文件系统,配置起来比较简单(ASM弄了半天也没配成功)

第十四、十五、十六步:默认。

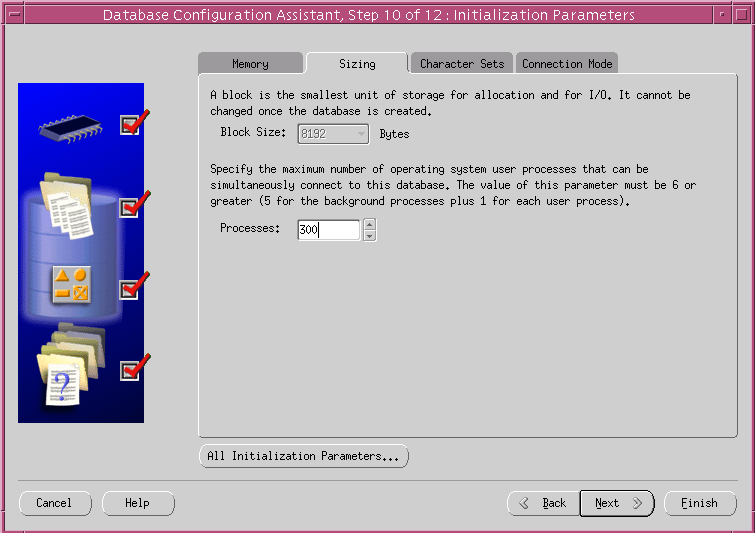

第十七步:内存等参数的设置

*内存:默认;进程:可以根据需要调整一下;字符集:ZHS16GBK;连接方式:Dedicated

第十九步:欲运行net manager程序,请执行

# /opt/oracle/product/10gr2/bin/netmgr

或者是

# cd /opt/oracle/product/10gr2/bin/

# ./netmgr

可完成对监听程序、服务名的配置。

欲停止或启动监听程序,请执行:

# /opt/oracle/product/10gr2/bin/lsnrctl stop

或者是

#/opt/oracle/product/10gr2/bin/lnrctl start

欲启动数据实例,请执行:

# sqlplus /as sysdba

登录,执行

#startup //editor 没有尝试!

启动数据库。

七)验证安装是否成功

1)验证是否安装成功:

# sqlplus system/yourpassword@yoursid

SQL> select * from tab;

2)关闭、启动正常

# sqlplus /nolog

SQL> connect /as sysdba

SQL> shutdown immediate

SQL> conn /as sysdba

SQL> startup

3)查看监听器状态

# lsnrctl status

分享到:

相关推荐

标题中的"adder8_adder_full_"可能是指一个8位全加器的项目或模块名,而描述中的"full-adder verilog and testbench code"表明我们将讨论使用Verilog硬件描述语言编写的全加器及其相关的测试环境。 全加器是一种能...

`h_adder`是这个VHDL设计的命名,可能代表Half Adder的缩写。`$h_adder`可能是为了突出这个概念,而`_vhdl_`则表明这是用VHDL语言编写的。 半加器的基本功能是接收两个单比特输入A和B,并产生一个和(Sum)以及一个...

This is a verilog code.It's function is 4 bit carry lookahead adder.

adder source code which is helpful in FPGA Design and Verification

16位Carry-Skip加法器(也称为Carry-Skip Adder)是一种优化了传统Carry-Lookahead Adder和Carry-Save Adder性能的设计,它在16位计算中特别有用,因为它能够显著减少执行加法操作时的延迟。这种加法器的设计主要...

超前进位加法器(Carry-Lookahead Adder,CLA)是一种在数字逻辑设计中用于提高加法运算速度的电路结构。它通过减少进位延迟来实现更快的加法运算,比传统的进位传递加法器(Carry-Propagate Adder,CPA)更为高效。...

在本压缩包“UVM_adder程序.zip”中,我们主要探讨的是Systemverilog语言中的一个关键应用领域——UVM(Universal Verification Methodology)框架。UVM是一种基于Systemverilog的标准化验证方法学,用于系统级集成...

全加器是数字电路设计中的一个基本组件,用于执行二进制数字的加法运算。...通过理解和分析"ADDER4B"的VHDL代码,可以学习到如何用硬件描述语言实现数字逻辑电路,并了解二进制加法在硬件层面上的具体操作。

### 可逆逻辑设计的16位进位跳过加法器 #### 摘要与背景 在数字集成电路的设计中,随着技术的发展与集成度的提高,能量消耗已成为一个至关重要的考虑因素。不可逆计算是导致能量损耗的一个重要因素。...

本项目“JAVA--Adder.zip”提供了一个小型的Java加法器,旨在实现基本的数字计算功能。这个简单但实用的工具可以帮助开发者进行快速的数值运算,尤其在学习和测试代码时非常方便。 在“JAVA--Adder.zip”压缩包中,...

本笔记将详细探讨加法器的设计,重点介绍进位选择加法器(Carry-Select Adder)的设计架构、工作原理以及在设计时的一些优化措施。 首先,加法器的主要功能是实现两个二进制数的相加运算,并计算相应的和(Sum)与...

Full Adder code very useful for development and anyone can use that in any project

本项目“adder+testbench”是一个基于Verilog实现的简单加法器,配合测试平台(testbench)进行功能验证。对于想要了解如何使用textio库进行输入输出操作的Verilog初学者来说,这是一个很好的学习资源。 首先,我们...

标题中的“add_32_bcd.rar_bcd adder_binary to bcd vhdl_java image editor_ra”揭示了这个压缩包包含的项目与多个技术领域有关,主要包括:32位BCD(二进制编码的十进制)加法器的设计,VHDL编程语言的应用,以及...

标题“adder16_adder16_”暗示了我们的重点是16位加法器,这在数字信号处理(DSP)系统中是至关重要的组成部分,特别是在构建滤波器时。标签“adder16”进一步确认了这一点,表明我们讨论的是与16位加法器相关的硬件...

在本项目中,我们探讨的是如何使用VHDL语言来实现半加器,并通过Testbench进行验证,这对于初学者来说是一个很好的学习案例。 VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种...

通过理解`select_adder.v`中的代码和参考`select_adder.jpg`的图形表示,我们可以学习到如何利用Verilog实现数字逻辑设计,并且了解到如何根据输入信号来动态改变硬件的行为。这对于理解和设计复杂的数字系统具有...

标题中的"adder_sub_struct.rar_adder_adder_sub_struct_sub_vhd_vhdl"表明这是一个关于VHDL编程的项目,具体是实现加法器(adder)和减法器(subtractor)的结构化设计。VHDL是一种硬件描述语言,常用于数字逻辑...

**Verilog BCD 加法器** 在数字电路设计中,BCD(Binary Coded Decimal,二进制编码的十进制)加法器是一...通过学习和分析"bcd_adder.rar"中的代码,开发者可以进一步提升其在数字系统设计和Verilog编程方面的能力。

在本实例中,我们关注的是一个名为"adder8_makefile_veri_verilog_slow7rj_VCS_"的项目,这涉及到数字逻辑设计的基础知识,特别是使用Verilog硬件描述语言(HDL)进行加法器的设计,并通过Makefile来管理编译流程。...